Facing Interfaces

Andrew Wilson, Editor

At the 2009 International Robots, Vision & Motion Control Show, Steve Kinney, chairman of the Automated Imaging Association (AIA) Camera Link committee and director of technical pre-sales and support with JAI, outlined two proposals to increase the bandwidth of camera-to-computer interfaces (see “Future Camera Link standards emerge,” Vision Systems Design, August 2009).

The first, CoaXPress (www.coaxpress.com), proposed by Adimec, is based on a line driver and equalizer chipset from Eqcologic and allows image data to be transferred over 50 m of coaxial cable at 6.25 Gbits/s (see Fig. 1). For higher speeds, more cables can be used in parallel.

The second, HSLINK, proposed by DALSA is based on InfiniBand 1x (or coax) cables for low-bandwidth applications (<300 Mbytes/s) or CX4 cables for higher-bandwidth applications (scalable up to 2100 Mbytes/s in 300-Mbyte/s steps) with each of the eight twisted pairs in the cable running at 3.125 Gbits/s. In addition, the option of using InfiniBand 12x cable will provide up to 6000 Mbytes/s using 20 differential pairs for video. At VISION 2009 in Stuttgart, potential developers and customers of products were given an opportunity to learn more about each of these standards.

CoaXPress emerges

To date, members of the CoaXPress consortium include Adimec, Eqcologic, Active Silicon, Components Express, AVAL Data, and Nippon Electro-Sensory Devices (NED).

At VISION 2009, many of these companies showed new products based on the proposal. These included Adimec’s Opal range of area-array cameras that use 1-, 2-, 4-, and 8-Mpixel interline CCDs from Eastman Kodak; Active Silicon’s Phoenix-CXP PCI Express interface board; and CoaXPress-compliant cables from Components Express. AVAL Data and NED have also joined the CoaXPress Consortium and will respectively introduce interface boards and linescan cameras to support the interface.

At present, the CoaXPress Consortium is developing the first draft of the CoaXPress specification and the Japan Industrial Imaging Association (JIIA) has agreed to host its standardization.

From Camera Link to HSLINK

DALSA’s proposed HSLINK standard is supported by DALSA, W.L. Gore, Silicon Software, and Stemmer Imaging. Products using HSLINK are cameras and interface boards made by DALSA. These include the company’s latest Piranha HS-12k, a 12,000 × 256-pixel CCD-based time delay integration (TDI) camera that runs at 93 kHz, producing 1.1 Gpixels at 12 bits per pixel per second or approximately 1.7 Gbytes/s of packed data.

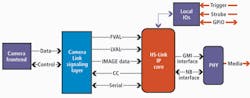

To transfer data from this camera to the PC, DALSA has announced the first HSLINK frame grabber, the Xcelera HS PX8, an x8 PCI Express board. To connect the camera to the interface board, a single CX4 connector is used. Unlike the CoaXPress interface, HSLINK builds on the concepts used in the Camera Link standard already adopted by numerous camera and frame grabber manufacturers (see Fig. 1).

In the design of the interface, familiar Camera Link data, frame valid, line valid, and clocking signals are clocked to an FPGA (the HSLINK IP core) that is used to packetize data and provide error handling and priority requests. To offer camera developers different ways to support the bandwidth of their cameras, DALSA has essentially developed three different interfaces from which the user can choose. All of these are based on the TLK313x series of serial transceivers from Texas Instruments that can also be embedded into the camera’s FPGA.

In the HSLINK proposal, two differential pairs are used as a control channel to handle camera triggering, GPIO, Ack/Nack, and command and idle messages. This control channel features a 300-Mbyte/s downlink from the camera to the frame grabber and a 300-Mbyte/s uplink from the frame grabber to the camera and is common to all HSLINK configurations.

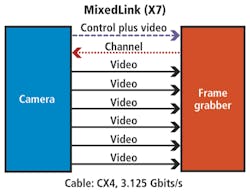

While camera control functions are packetized into a 9-bit interface (NBI), video data are packetized into a Gigabit Media Independent (GMI) interface for the GMIILink variant. In the highest bandwidth configuration, known as MixedLink mode, two four-channel TI serial transceivers allow eight differential pairs to transmit eight channels of camera control and image data (see Fig. 2).

In the MixedLink configuration, image data is added to the downlink control channel of the GMIILink. Using CX4 cables with eight differential pairs, this allows speeds of up to 2.1 Gpixels/s to be obtained on a single CX4 cable. In other configurations, such as NBILink (x1), a single control channel is used and image data are added to the 300 Mbytes/s downlink. In NBILink x2, a second video channel is added to NBILink x1 to achieve 600 Mbytes/s. Such configurations allow cameras with different bandwidths to be supported.

Comparisons and compatibility

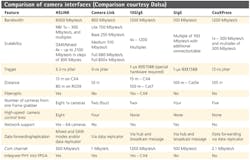

To effectively promote the HSLINK proposal as a standard, DALSA will offer camera and frame grabber vendors reference designs for the interface and FPGA code. Of course, comparisons between CoaXPress and HSLINK will be made (see table).

“At multilane bandwidths for higher speeds, HSLINK is more cost effective than CoaXPress because the equalization function is built into the TI SerDes and therefore doesn’t require additional equalizer ICs as the bandwidth increases,” says Mark Butler, product manager at DALSA. “At HSLINK (NBILink x1), which is more comparable to the CoaXPress solution, the costs are similar. In this case, HSLINK would employ a single transceiver device from the TLK313x family, which has been tested by TI to achieve 80-m distance on RG6 coax cables. While the Ecqologic chip does enable transmission to 105 m using a single coax cable, the higher-bandwidth capability of the HSLINK uplink is lost when using the lower-bandwidth uplink of CoaXPress.”

Company Info

Active Silicon

Iver, UK

www.activesilicon.com

Adimec

Eindhoven, the Netherlands

www.adimec.com

AVAL Data

Tokyo, Japan

www.avaldata.com

Components Express

Woodridge, IL, USA

www.componentsexpress.com

DALSA

Waterloo, ON, Canada

www.dalsa.com

Eastman Kodak

Rochester, NY, USA

www.kodak.com

Eqcologic

Brussels, Belgium

www.eqcologic.com

JAI

San Jose, CA, USA

www.jai.com

Japan Industrial Imaging Association

Tokyo, Japan

www.jiia.org

Nippon Electro-Sensory Devices

Osaka, Japan

www.ned-sensor.co.jp

Silicon Software

Mannheim, Germany

www.silicon-software.com

Stemmer Imaging

Puchheim, Germany

www.stemmer-imaging.de

Texas Instruments

Dallas, TX, USA

www.ti.com

W.L. Gore

Landenburg, PA, USA

www.gore.com