MARCH 24--Previous attempts at offloading algorithms into parallel and programmable hardware architectures have fallen short of the mark due to technical barriers, price, or lack of suitable and easy-to-use design tools.

On Wednesday, April 5, at the Embedded Systems Conference in San Jose, CA, Celoxica (Abingdon, Oxfordshire, England; www.celoxica.com) will join AMD (Sunnyvale, CA; www.amd.com) and Xilinx (San Jose, CA; www.xilinx.com) to show the changes now occurring to make hardware acceleration commercially viable using AMD's Opteron processor, Xilinx's Platform FPGA technology, and Celoxia's programming environment.

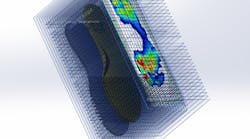

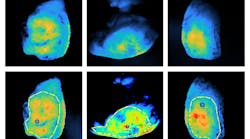

"The high-performance computing industry is beginning to leverage the potential of Virtex-4 FPGAs as a coprocessor to devices such as AMD's Opteron. Algorithms embedded in large applications can be accelerated improving performance for scientific and medical imaging systems," says Krishna Rangasayee, a senior director at Xilinx.

The technical training program at the Embedded Systems Conference (www.embedded.com) includes the classes and tutorials, a microprocessor summit, and a series of design seminars covering topics such as analog and power, DSP performance, Linux, consumer video, and wireless networking.