The emergence of high-speed cameras and interfaces creates new opportunities and challenges for developers of machine vision systems. While embraced by numerous camera and frame grabber vendors, the emergence of the CoaXPress (CXP) standard, for example has led to a number of cameras and frame grabber offerings from numerous suppliers (see "CoaXPress cameras and frame grabbers tackle high-speed imaging", Vision Systems Design, January 2014, http://bit.ly/RQrAQD).

To embrace this high-speed interface, systems integrators can use CXP to Camera Link or Camera Link to CXP converters that allow developers to leverage existing Camera Link frame grabbers with newer CXP cameras. Such converters also allow Camera Link cameras to take advantage of the longer camera to computer distances offered by the CXP standard.

While using such converters is effective, they are limited by the maximum bandwidth of the Camera Link standard and add additional expense to a system.

Rather than take such an approach, many systems integrators may prefer to simply abandon the Camera Link standard and purchase dedicated CXP cameras and frame grabbers.

This task may require additional software engineering since any image pre-processing routines written to run the FPGA of one frame grabber will not necessarily be easily ported to a newer board.

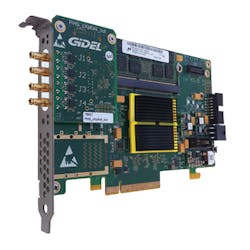

To alleviate this task, Gidel (Santa Clara, CA, USA; www.gidel.com) has introduced a modular image processing board, the ProceV, a Gen3, x8 PCI Express board based on Altera Stratix V FPGA that allows developers to add many different types of camera interfaces and data output formats to meet the needs of a range of applications.

To implement these different I/O devices, Gidel has taken advantage of the on-board high-speed transceivers on the FPGA and developed a range of modular I/O boards for the ProceV base board. These include image capture boards that support the Camera Link, CXP, SDI, HDMI and 100Gbit Ethernet standards.

To capture images from a Camera Link-based camera, for example, the company's PSDB_CL/ CL_IO daughterboard supports Base, Medium, Full and 80-bit configurations of the standard and twelve general purpose I/O channels.

Those wishing to interface CXP cameras to the board can use Gidel's PHS_cXp6x4 daughterboard to connect four 6.125Gbit/s CXP channels, while an additional eight CXP channels can be added if required. To support these data rates, the board features up to 16 GBytes of double data rate DDR3 memory that can store image data at rates of up to 19.2 GBytes/s.

As well as supporting numerous camera input standards, the board also offers systems developers modular output boards that can support Camera Link, CXP, 100Gbit Ethernet and SATA interfaces. By taking this modular approach, the board can be configured for a number of different applications.

Should a third-party frame grabber vendor require a Camera Link or CXP-based simulator, for example, the ProceV board can be configured to output Camera Link or CXP signals and Gidel's ProcCamSim simulator application used to generate image test patters. In high-speed imaging, multiple CXP cameras can be interfaced to the board and streamed to up to eight SATA drives at data rates of 6Gbit/s per drive.

Those wishing to program the on-board FPGA can choose from a number of different development tools including the company's own PROC_HILs software that allows Simulink designs to run on FPGAs and Altera's Quartus II design software.

Vision Systems Articles Archives