Imaging with Camera Link

Currently, the fastest Camera Link boards can acquire, preprocess, and transfer images or analysis results to system memory at sustained DMA rates to 360 Mbytes/s.

Around 1987, the growing user community started pushing the envelope with camera manufacturers. International standards, such as CCIR, and certain market segments began to push the camera pixel rate into the 12.5- to 14.3-MHz range. These popular pixel rates evolved to support 640 X 480 RS-170 and 768 X 576 CCIR "square pixels" for the rapidly growing metrology (measurement) market. Rising to this occasion, frame-grabber and image-processor manufacturers began offering boards with selectable and variable pixel clocks to meet this new design challenge.

Around 1990, the industry's unyielding appetite for higher spatial resolutions, greater dynamic range, and improved data integrity brought on the era of the digital "megapixel" camera. But much to their chagrin, imaging-processing and machine-vision system designers found that the cameras that solved spatial resolution, dynamic range, and data-integrity problems could only output pixels at 10 MHz due to limitations in RS-422 transceiver devices. The 30-frame/s frame-grabbing standard to which designers had grown accustomed was suddenly out of grasp. Then, for at least two years, the 7.5-frame/s rate became a high-resolution "digital video" fact of life that the "megapixel" imaging user had to endure. In this time frame, frame-grabber and-image-processor manufacturers jettisoned their A/D converters and began equipping their boards with RS-422 parallel digital front ends. From that time forward, the "digital video revolution" continued to evolve.

The pain of low frame rates was somewhat debilitating for the industry. By 1992, the solution from camera manufacturers was straightforward—just add more parallel taps to the camera. The first solution to this problem was a two-tap camera that increased the effective data rate by a factor of 2X, or 20 MHz. This presented a new performance benchmark for frame-grabber and image-processor manufacturers in terms of on-board memory bandwidth. In this time period, memory and internal data-switching architectures also needed to be redesigned to handle the 20-MHz data rates. Moreover, 100-ns memories needed to be replaced by 50-ns memories, 10-MHz cross-port/point switches needed to be redesigned to handle 20-MHz data rates, and so forth.

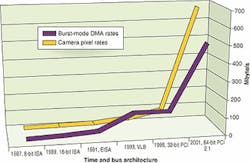

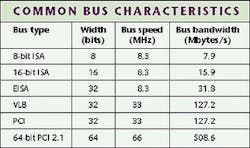

Four-tap camerasBy 1993, commercial four-tap cameras made their debut. These cameras represented yet another challenge to increase memory capacity and processing bandwidth by a factor of 2X. This 40-MHz performance milestone necessitated major redesigns of memory, data bus, and processing chips (for example, 20-ns memories, and 40-MHz convolvers) for frame-grabber and image-processor manufacturers. In addition to handling the increased bandwidth requirements, the four-tap camera also posed significant mechanical packaging challenges for board-level manufacturers as they had to find a way to terminate upwards of 96 wires in a space that was less than 2 sq. in. on the back panel of an ISA/EISA card. Because of the magnitude of these design challenges, it took about a year before viable board-level digital-image-processing platforms were available to accommodate the new rank of high-performance image-processing users.While imaging bandwidth requirements continued to spiral upward, the need for larger memory buffers for interim storage started to become a significant cost factor for users. The EISA/ISA bus of the day couldn't get image data off the board and into host memory fast enough with its 31.8-Mbyte/s maximum bandwidth (see table). More on-board memory and processors were needed.

PCI bus emergesIn 1994, the imaging industry eagerly awaited the arrival of the PCI bus, as this bus offered the promise of being able to cost-effectively handle many of the new 40-MHz bandwidth requirements. The PCI bus 127-Mbyte/s bandwidth was a huge enabler of the memoryless frame grabber. After the 32-bit PCI bus took hold in 1995, manufacturers were essentially given a comfortable bandwidth margin and a reprieve from increased memory costs that would last well into the late 1990s. From that time host-based image-processing and analysis software running with low-cost frame grabbers and Intel processors began to grow at an incredible rate. This marked the beginning of the end of the high-cost, $20,000 image-processing machine-vision engine and opened up huge growth in the low-cost frame-grabber market segment.By the late 1990s, device manufacturers still had not solved the "spaghetti cluster" of wires coming from the cameras and terminating at the back of the PC. The additional cost of high-density connectors, expensive custom multiwire cables, and large termination panels started to wash out the savings that were gained from the reduced memory costs offered by the advent of the high-bandwidth PCI bus. Something had to give, especially with eight-tap cameras (160-wire terminations) on the horizon.

Camera Link momentumTo overcome most of these design and user problems, a focused initiative from Pulnix America (Sunnyvale, CA, USA), a consortium of interested manufacturers, and a newly organized Automated Imaging Association (AIA) camera committee joined forces. From all of their hard work, a newer, cleaner, and faster camera-interface standard was introduced—Camera Link.Designed around the low-voltage differential-signaling (LVDS) general-purpose interface standard known as ANSI/TIA/EIA-644, the new Camera Link interface standard could achieve a theoretical maximum transmission rate of 1.923 Gbits/s into a lossless medium. What once took upward of 200 wires of termination was now efficiently organized onto two industry-standard 26-pin connectors. Because Camera Link's transmission method required fewer conductors, it provided a cleaner, ultrahigh-bandwidth interconnection between high-performance megapixel cameras and frame grabbers/image processors.

This Camera Link standard offers three levels of performance—Base, Medium, and Full configurations—enabling it to support everything from 640 X 480 1-tap to n (k) X m (k) 8-tap line- and area-scan cameras. Providing support for cameras with up to eight taps (and even 10 taps in the near future), each running at up to 85 Mbytes/s, the new image-acquisition bandwidth ceiling was quickly escalated to 680 Mbytes/s.

During 2001 more than a dozen frame-grabber and image-processor manufacturers quickly jumped on the Camera Link bandwagon and began redesigning their current digital frame-grabbers with the new LVDS/RS-644 interface transceivers. Most of these early boards focused only on the Base configuration, which took advantage of only about 60 Mbytes/s of the total 680-Mbyte/s bandwidth capacity.

To fully leverage Camera Link's 680-Mbyte/s bandwidth capability, board manufacturers quickly realized that the 127-Mbyte/s maximum burst-mode DMA transfer rate of the 32-bit/33-MHz PCI bus was not fast enough to sustain the image data rates required by the new high-performance Camera Link cameras. One by one, frame-grabber manufacturers such as Datacube, DataCell, Alacron, and EDT began to introduce Camera Link boards with 64-bit/66-MHz PCI 2.1 capabilities to increase the total bandwidth capacity of their offerings.

Today, the fastest Camera Link boards can acquire, preprocess, and transfer images or analysis results to system memory at sustained DMA rates of up to 360 Mbytes/s. Internally, such boards can also stream image data to on-board PC-2100 memory at rates of up to 1 Gbyte/s, and they can typically offer on-board memory capacities of up to 2 Gbytes. All of these resources eliminate bottlenecks and enable higher image-scanning speeds, especially in high-speed continuous web-inspection applications where "guaranteed no missing lines" is mandatory.

However, there is still disparity between the 680-Mbyte/s acquisition bandwidth of Camera Link and the maximum sustained (not burst) DMA transfer rates of 360 Mbytes/s (burst mode) for the 64-bit/66-MHz PCI bus 2.1 (see figure). So, traditional digital frame grabbers without substantial on-board memory buffers or on-board processing resources (for example, FPGAs, DSPs, and MIPs) for performing image data analysis and reduction will continue to find it difficult to gain market acceptance in the high-end Camera Link space. After the computer industry embraces the 64-bit/133-MHz PCI bus, industry trends are expected to change again, which frame-grabber manufacturers have come to live.

Tom Hospod is vice president of marketing and business development at Datacube Inc., Danvers, MA 01923.