Third-party IP speeds system development

For a number of years, high-volume gate-array manufacturers such as Altera (San Jose, CA, USA; www.altera.com) and Xilinx (San Jose, CA, USA; www.xilinx.com) have offered intellectual property to their customers as a means of speeding the development of FPGA-based systems. Notably, these companies offer a number of different intellectual-property products such as JPEG, MPEG, and H.264 encoders and decoders targeted toward the lucrative broadcast and surveillance markets.

In the machine-vision market, however, one of the most successful suppliers of intellectual property is Pleora Technologies (Kanata, ON, Canada; www.pleora.com), a company whose iPORT series of Gigabit Ethernet (GigE) connectivity products can be found in more than 90% of today’s commercially available GigE Vision-based cameras. Recently, at The Vision Show in Boston, MA, USA, the company unveiled its third-generation in-camera internet protocol (IP) engine, a 42 × 42-mm board known as the iPORT NTx-Mini developed for small form-factor cameras.

Consuming 1.45 W, the NTx-Mini consists of a main board that interfaces to an optional AdaptRBoard and FlexEBoards. While the main board manages the conversion of imaging data to IP packets at 1 Gbit/s, the AdaptRBoard provides TTL GPIO and RS-232 capability. Power and programmable-logic-controller functions are provided by the optional FlexEBoard.

Seeing the success of Pleora’s GigE products, other companies are also looking to enter the market, most notably GigaLinx (Hod-Hasaron; Israel; www.gigalinx.net), which also chose the show to demonstrate an in-camera IP engine called the GigE Connect EM2-1000T IP Engine. Like Pleora’s products, the EM2-100T is designed to enable industrial cameras to take advantage of a ready-made IP engine specifically developed for industrial cameras.

Integrating both a camera power supply and the GigE engine in a single board, the EM2-1000T directly interfaces to a CCD/CMOS image sensor board, allowing camera developers to offer two-board camera configurations. GigaLinx chose the show to demonstrate a 1.8-W power consumption, 40 × 55-mm footprint prototype camera based on a 30-frame/s VGA image sensor from Micron Technology (Boise, ID, USA; www.micron.com) to highlight the capability of the interface. According to Yuval Nahum, vice president of sales and marketing at GigaLinx, the product will be offered as a full-scale reference design to interested camera manufacturers.

While companies such as Pleora and GigaLinx pursue development of camera interface standards, others are looking to leverage the same idea to perform sensor interfacing and image-processing functions for camera designs. Although not exhibited at The Vision Show, camera front-end intellectual property from Bitec (Chippenham, UK; www.bitec.ltd.uk) allows camera developers to interface CMOS and CCD cameras to an Altera FPGA (see Fig. 1). Using a line buffer, the interface is designed to provide an interface between the camera and a back-end processor. As the line-buffer automatically adapts to the camera resolution, the back-end application can resize or window the image in real time. A Bayer demosaicing algorithm is then performed to produce an interpolated RGB output.

While such front-end interfaces provide a simple way to interface cameras to other circuitry, processing these images is a more complex task. Relatively unknown companies such as Apical Imaging (London, UK; www.apical-imaging.com), Digital Design Corporation (DDC; Arlington Heights, IL, USA; www.digidescorp.com), and Tenesix (Littleton, MA, USA; www.tenesix.com) are looking to fulfill a market need by developing intellectual property in the form of image-processing pipelines.

Based on proprietary algorithms, Apical image-processing pipeline functions include dynamic range correction, color processing, image sharpening, and noise reduction. While many of these algorithms are found in consumer-based products, they will also find use in security and defense applications where image enhancement algorithms are in great demand.

DDC has also developed intellectual property in the form on an image-processing pipeline known as the DDC FLIR. This allows developers to build a complete embedded camera or image-processing product using either ASICs or FPGAs. This pipeline contains a number of image-processing functions that include decoders for digital and digitized analog video sources with de-interlacing, color space conversion, and rate adaptation an integrated DDR controller for performing rate conversion and an output encoder with color space conversion and gamma correction.

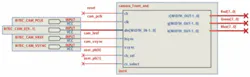

At The Vision Show, Arun Chaddha, president of Tenesix, showed camera vendors his latest FPGA-based image-processing pipeline (IPP), intellectual property that, says Chaddha, can be customized for medical imaging, surveillance, and 3-D sensing applications. Available for both Xilinx and Altera FPGAs, the IPP consists of an image processing pipeline and a display pipeline (see Fig. 2).

“This architecture,” says Chaddha, “allows a number of functions including gain and offset correction, demosaicing, gamma correction, smoothing, and sharpening to be performed at frame rates.” Customer-specific algorithms such as programmable filters and fixed and adaptive thresholding algorithms can be inserted in-between the sensor pipeline and the display pipeline. As the display pipeline uses external DDR2 memory, processed images can be synchronized to match DVI, VGA, S-Video, and composite video display formats. The pipeline is flexible enough to accommodate sensors with different resolutions and frame rates.