Modular architectures embed frame-grabber flexibility

Systems-integrator demands for the next generation of PC-based machine-vision systems are anticipated to include faster host bus transfer rates, standard high-speed analog and digital camera interfaces, and expansion flexibility. To meet these demands, a number of 64-bit, 66-MHz PCI boards are now being introduced that provide both Camera Link and low-voltage-differential-signaling (LVDS) interfaces and intelligent input/output (I/O) controls.

Whereas many companies are designing point products to solve specific machine-vision and image-processing problems, Coreco Imaging (Billerica, MA; www.imaging.com) is taking a more systems-based approach with modular products that embed multiple image-capture, process, and display boards in a single chassis. As part of the introduction of its X64 series of next-generation 64-bit, 66-MHz frame grabbers, Coreco plans a series of such modular products designed to interface to analog, LVDS, and Camera Link-compatible standards. Initially, the company is offering the X64-CL series of Camera Link-compatible frame grabbers in two versions: a dual-Base configuration (or one Medium configuration) and a Full configuration.

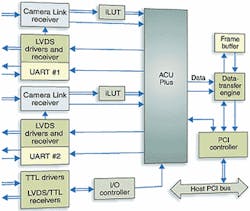

At the core of the X64-CL series is the acquisition control unit plus (ACUPlus). By acting as an intelligent grab control, this FPGA-based unit performs all camera control functions, such as asynchronous reset, tap reversal, and concurrent acquisition from multiple format cameras. Programming the device using the company's Sapera software also allows the ACUPlus' pixel-packing function to accept data from any Camera Link-compatible camera and output these data in the correct memory-mapped order for the PCI interface.

To control external devices such as I/O controller boards, the X64-CL I/O control section features eight in and eight out lines of TTL control that can also be configured using Sapera as eight lines of LVDS control. To transfer data between the frame grabber, using up to 256 Mbytes of on-board memory and the 64-bit, 66-MHz PCI interface, the board comes with another custom FPGA called a data-transfer engine (DTE). Using scatter-gather DMA to off-load memory transfer functions from the host CPU, the DTE defines the configuration of nonstandard cameras as data are read from the individual camera taps.

When multiple linescan Camera Link cameras are used, for example, the DTE can be programmed under Sapera to realign and remove any overlap that might exist among multiple cameras. The X64-CL series of Camera Link-compatible 64-bit, 66-MHz frame grabbers will be closely followed by the higher-end X64CLP versions.

These products, to be introduced at this year's Vision Show West (Nov. 19-21; Santa Clara, CA), will also include the X64-CLP series. This series includes a dual-Base configuration and one Medium configuration frame grabber (the X64-CLP Dual), a quad-Base configuration and dual-Medium configuration frame grabber (the X64-CLP Quad), and a dual-Full configuration frame grabber (the X64-CLP-Full). To support these products, the company is also looking to introduce a series of processing modules that will interface to the frame grabbers using the on-board DTE. In these implementations, the DTE interfaces to other individual processing elements such as pixel processors and Bayer color conversion modules over a high-speed 528-Mbyte/s bus.

Correction:On p. S19 of the Camera Link supplement, mailed with the May issue of Vision Systems Design, the EPIX product designation should be PIXCI.