PCI Express sets new high-speed interface standard

By Steve Moore and Chris Youman

The original PCI standard was created in the early 1990s to offer a high-performance pathway for PC graphics, and at the time of its inception the 133-Mbyte/s bandwidth of the 32-bit/33-MHz spec was truly impressive. Since that time, there have been several extensions to the spec, with the current version offering approximately 1 Gbyte/s of raw bandwidth; however, the usable bandwidth is less than this because of the overhead of a shared bus.

In addition to overhead, the shared-bus nature of PCI raises a connectivity issue. Because there are electrical restrictions on how many physical loads can be attached to any PCI node, a family of products called PCI-to-PCI bridges has been spawned whose purpose is to physically isolate subsystems that would otherwise present an overly large electrical load on the system.

BRIDGING THE GAP

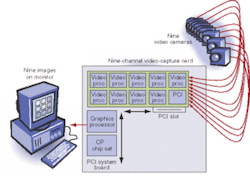

As frame rates and camera resolution increase, bandwidth requirements are increasing dramatically, especially in high-speed image acquisition in scientific and instrumentation applications that require high frame rates. The number of imaging devices handled by each subsystem also is increasing. Having multiple cameras or display devices strains both the bandwidth and the physical connectivity of these subsystems. In a video-capture system with nine cameras and a trio of three-channel PCI video-capture cards, for example, bandwidth and connectivity are two distinct obstacles that need to be overcome (see Fig. 1).

PCI-to-PCI bridges, such as the PCI 6000 series from PLX Technology (Sunnyvale, CA, USA; www.plxtech.com), allow imaging systems to be expanded in terms of both capture and display. In each case, the camera or display interface will normally control a single camera or output device, and, to offer multidisplay capability, the designer isolates the chips behind a PCI-to-PCI bridge. The bridge then shows only a single load to the main system, thus conforming to the specification. The software support for these devices is built into the operating system and is thus transparent from an application perspective.

Bridge devices such as the PLX PCI 6156 can handle as many as 10 loads on the secondary port, with the ability to master the bus for each load individually (see Fig. 2). The primary and secondary ports can operate at different speeds in an asynchronous manner, enabling the aggregation of a number of lower bandwidth data streams into a high-bandwidth pipe. As the bandwidth needs of the system increase, moving to a PCI-X (64-bit/133-MHz) bridge allows the designer to provide full physical- and software-backward compatibility with the PCI infrastructure.

There is a limit to how much a shared-bus architecture such as PCI can be expanded, but systems developers continually strive for greater bandwidth and loading. A logical step in the evolution of imaging systems is the migration to the next-generation serial version of PCI called PCI Express. PCI Express offers bandwidth and connectivity expansion well beyond PCI, but remains 100% software-compatible with the established PCI architecture.

IMAGE SENSING

Recent advances in image-sensing technology are placing greater demands on interconnect bandwidth. As the number of pixels increases, so does the requirement for processing power and the demands on memory capacity and bandwidth. Depending on the amount of compression and the frame rate, interconnect bandwidth requirements for current systems can range from ten to several hundred megabytes per second—all handled effectively by PCI or PCI-X.

For example, a 1-Mpixel image that is compressed by two-thirds and refreshed at a high data rate for a scientific application would require on the order of 300 Mbytes/s. New image sensors capable of 4-Mpixel resolution, however, can require several gigabytes per second of throughput. An 8-bit-pixel sensor running at 30 frames/s, for example, requires 1.2 Gbytes/s before compression. Scientific-imaging applications may require frame rates on the order of 10 to 20 times higher (1000 frames/s). An image sensor capable of 4-Mpixel resolution could require 1.3 Gbytes/s of interconnect throughput at such high frame rates after compression. This performance metric goes beyond PCI-X's even theoretical maximum capacity of 1 Gbyte/s at full 64-bit/133-MHz capability.

PCI Express is an ideal interconnect technology for next-generation vision systems such as frame grabbers because of its increased bandwidth, quality of service, and flow-control features. With 2.5 Gbytes/s of raw throughput per lane in both the transmit and receive directions, PCI Express can provide the bandwidth needed to address the latest imaging applications. A link that offers eight lanes can realize a throughput of 2 Gbytes/s streaming in one direction after accommodating the associated 8-bit/10-bit clock overhead.

PCI Express also allows for up to eight traffic classes for prioritization of data flow, and PCI Express switches with more than one virtual channel will allow a high-priority channel to be dedicated to imaging data. Finally, PCI Express switches and bridges offer credit-based flow-control mechanisms that help manage congestion in an imaging system handling large amounts of data.

PCI Express offers a significant amount of bandwidth headroom for demanding imaging applications and requires fewer pins than conventional PCI or PCI-X interfaces for any particular bandwidth. A single 2.5-Gbyte/s link only requires four wires in the form of an LVDS transmit and receive pair and can be scaled as necessary to offer a low pin count per megabyte, regardless of the bandwidth required in the system.

Several components and systems will be introduced this year, including motherboard slots, notebook card slots, 3U and 6U chassis, and card subsystems for embedded applications. Available silicon will include processors and chipsets, graphics controllers, LAN controllers, and storage protocol devices. The multitude of switching and bridging devices from companies such as PLX will further enable systems with the serial standard.

PCI Express offers more than just module slot capability, since its serial nature allows it to traverse backplane and cable implementations. The working group defining PCI Express over cabling has started to model implementations that span several meters over a copper cable. This ability to carry large amounts of data through a thin, serial connection will prove useful in joining remote image sensors to processing or display systems.

FEEL THE BENEFIT

It is relatively straightforward to upgrade existing PCI or PCI-X based frame grabber boards to reap the benefits of PCI Express. Placing an existing PCI-based design behind a PCI Express-to-PCI/PCI-X bridge provides a way to enhance the adapter design and take advantage of the multitude of PCI Express slots soon to be available. For example, a PCI Express-to-PCI-X bridge with a four-lane PCI Express port provides the bandwidth to handle any PCI-X-based image application with fewer pins and added functionality.

To confirm that PCI Express-to-PCI/PCI-X bridges are useful in imaging, PLX has demonstrated its bridge design using hardware-emulation boards developed for verification and interoperability testing. PLX connected a digital-image sensor to a PCI-based I/O board, enabling data to be transmitted to a PCI Express bridge emulation card via a standard cable connector. The 1M copper cable was connected on the other end to an identical PCI Express bridge emulation board, managed by a host CPU and display system.

STEVE MOORE and CHRIS YOUMAN are senior product-marketing managers at PLX Technology, Sunnyvale, CA, USA; www.plxtech.com.