Twenty sixteen was yet another outstanding year to be a participant and spectator in the CMOS image sensor (CIS) marketplace - with significant advancements in devices and architectures. Viability of stacked CIS in high-volume applications has been proven, and is expected to dominate CIS advances for the next 3-5 years.

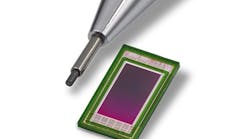

Stacking delivers a smaller footprint for the CIS and processor combo and overall lower power consumption due to more efficient partitioning of processing functions between the two die. A smaller footprint has advantages in many markets, and is absolutely critical in applications such as endoscopy. In addition, the CIS die can be fabricated in a simplified process that's optimized solely around the pixel performance and yield, resulting in significantly lower noise, defect densities, and non-uniformities. An ultimate goal is to create more advanced pixels by local high density interconnects. This allows the pixel to be split between the upper and lower die - for example, to allow global shutter pixels with excellent parasitic light (in)sensitivity.

Stacking still faces challenges starting with higher non-recurring engineering (NRE) costs for the following: a) the cost of the stacking process itself, b) costs of designing two die with the associated complications of co-simulation and co-verification of designs that might use different fabrication processes, c) the need for two mask sets, and d) the added complexities during characterization, qualification, and production.

In certain applications, stacking can also increase the combined sensor/processor price over non-stacked approaches. For example, in using wafer-level stacking, the final yield of the bonded pair is a product of the yield of each die. Also the two stacked die typically need to be the same physical size. This can be a problem for very large sensors (full frame 35mm, APS-C) and very cost-sensitive applications (i.e. IoT), where it can be difficult to find an economic balance in die area. Again, we expect that these problems will find solutions with advances in device architectures and smart choices in process selection.

A big part of our work at Forza Silicon is focused on the professional/prosumer camera markets. While there has been a great deal of activity in high-resolution video (4K and above), the once-humble cell phone camera has stolen the limelight from the DSLR/digital still camera. But expect a strong response from the "still" camera market with very un-still like high-speed 4K video and higher dynamic range - with performance that might also challenge the incumbents in the digital cinema and broadcast markets. An exciting new trend may have started with the announcement of a medium-format camera aimed at non-professional photography enthusiasts. Ultimately the pricing of this camera will determine if we will see a significant technology push for extra-large format sensors in the near future.

We also continue to see a lot of activity in the unconventional imaging applications. Various markets, including automotive and augmented reality, are driving the need for 3D image sensors, which have been addressed by Time-of-Flight sensors. However, these continue to struggle with ambient light and the need for an injection of significant near-infrared light power into the scene. These problems, and their cost impact, must be overcome before this can become a significant market.

Barmak Mansoorian,

President & Co-Founder, Forza Silicon